BC3 VDSL (XDSL) Modem (ESPRIT 26298)

The target of the project has been the design and implementation of a VDSL modem discrete multitone (DMT) at 23Mbits/sec. The modem has an ATM interface communicate with the computer. It involves two FPGAs ALTERA APEX EP20K600EBC652-1XES NAAE610019C, two Lucent 16210 DSPs and a Motorola MPC860 microprocessor. The first ALTERA realizes the transmitter and the second the receiver. DSPs are responsible for synchro and high level parameter management, while the microprocessor performs the system housekeeping.

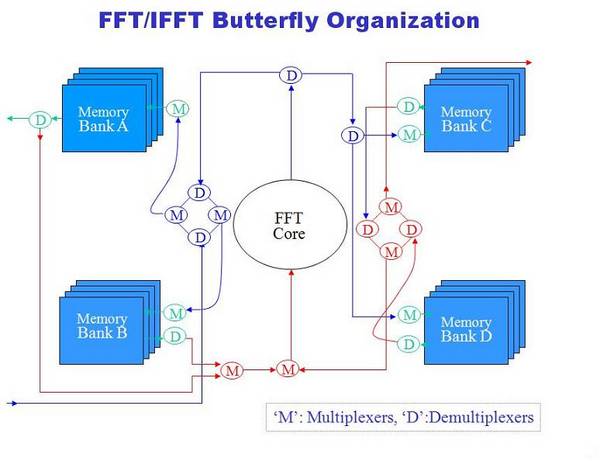

DST has designed and implemented the digital baseband processing pipeline of transmitter and receiver blocks within the two FPGAs. The following image shows the digital baseband processing module of the VDSL modem.