Frequency Analyser (Institute for Accelerating Systems and Applications-Internal Project 2004-2006)

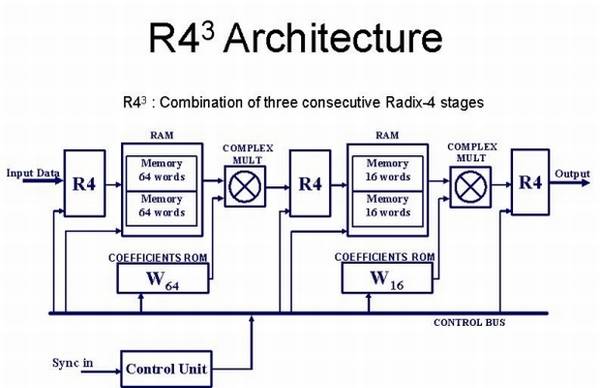

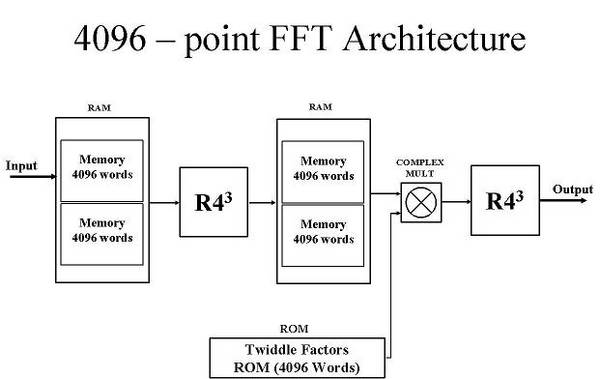

The Frequency Analyzer has been designed for 200 MHz bandwidth. The bandwidth has been divided into four bands of 50 MHz each. A 4096 complex points FFT architecture has been studied and designed to acomodate the computations of each 50 Mhz band. The high performance of the VLSI-based FFT architecture is key to the system because it meets the hard real-time constraints at low silicon area and low power compared to CPU-based solutions. In order to achieve these goals, DST presented a novel VLSI FFT architecture based on combining three consecutive radix-4 stages to result in a 64-point FFT engine called the R43 Engine. Cascading these 64-point FFT engines consequences an improved architecture design featuring certain characteristics. First, it can efficiently accommodate large input data sets in real time. It also simplifies processing requirements due to the radix-4 calculations. Finally, it reduces memory requirements and latency to one third compared to the fully unfolded radix-4 architecture. Two different implementations validate the architecture efficiency: a FPGA implementation of a 4096-point FFT achieving a throughput of 4096 point/20.48 usec, and a VLSI implementation sustaining a throughput of 4096 point/3.89 usec.

Paper Output

- K. Manolopoulos, K. Nakos, D. Reisis, N. Vlassopoulos, V.A. Chouliaras, "High Performance 16K, 64K, 256K VLSI Systolic FFT Architectures", pages: 146 - 149, Marrakesh, December 2007, IEEE International Conference on Electronics, Circuits and Systems

- K. Babionitakis, K. Manolopoulos, K. Nakos, D. Reisis, N. Vlassopoulos, V.A. Chouliaras, "A High Performance VLSI FFT Architecture", pages 810-813, December 2006, IEEE International Conference on Electronics, Circuits and Systems

- K. Babionitakis, K. Manolopoulos, K. Nakos, D. Reisis, N. Vlassopoulos, "A Memory Efficient, Low Power Fast Fourier Transform Architecture", Loughborough UK, September 2004, The IEE, ACM SoC Design, Test and Technology Postgraduate Seminar